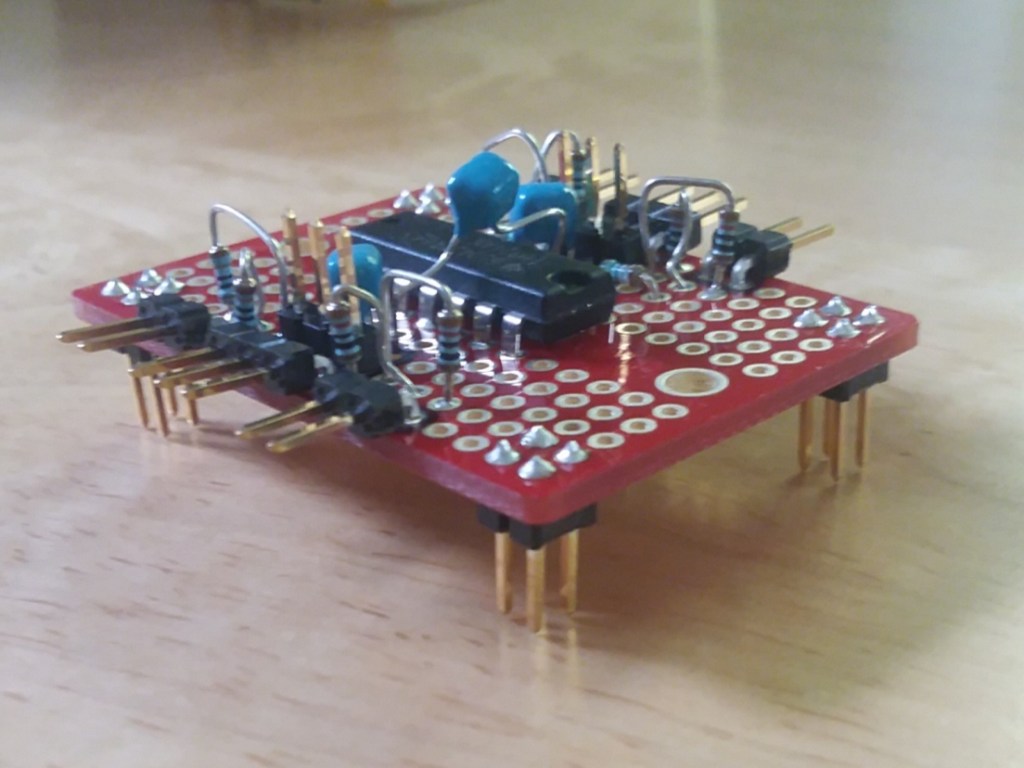

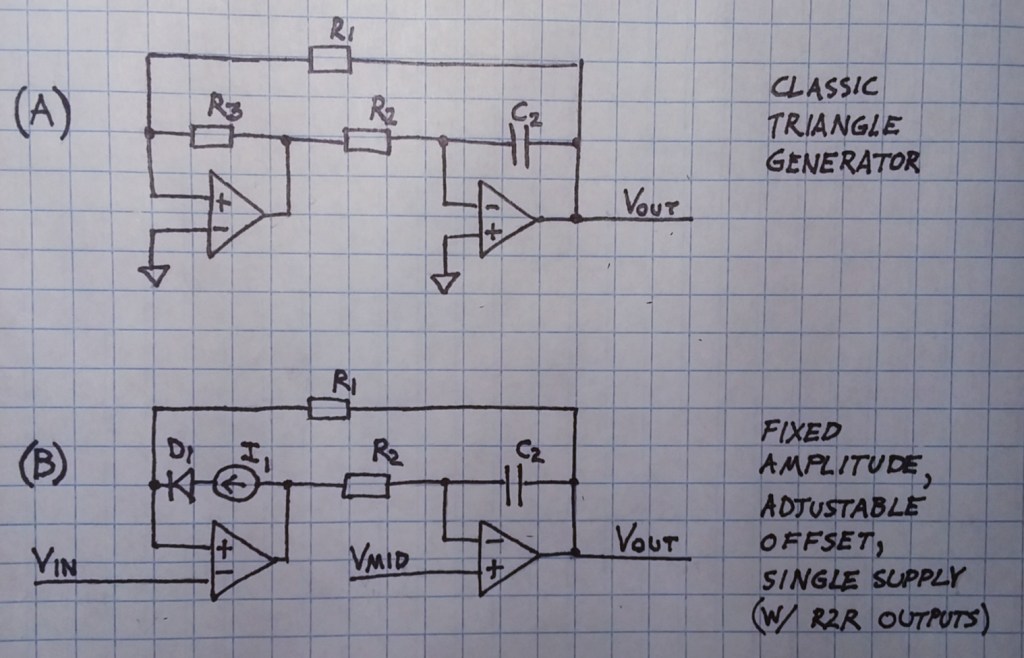

TLDR; capacitor C180 was added to the circuit below to make it happy.

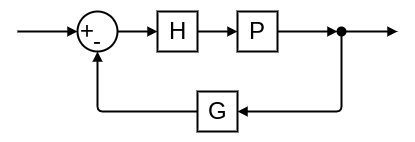

Background: 24V PLC digital signal driver (spec: up to 15mA sourced or sunk, 100kHz, idiot proof vs shorted field wiring, able to tristate for troubleshooting by integrators). The driver IC I had been using became unavailable amid this year’s supply chain trainwreck. I thought, no problem, just throw down a few transistors.

The driver is shown below, omitting a couple of ESD/TVS protection and termination parts. SIG_VCC is the “24V” supply. The logic input comes from a 5V circuit, and in that case SIG_VBB is 2.5V. The input does level-shifting and passes on the tristate condition, or close enough for PLC purposes.

Without C180, among other things, there was cross-conduction from delayed turn-off (caused by dV/dt on the output pushing/pulling current through the output transistor’s base-collector capacitance — pretty much Miller effect). Other fixes would be to cascode, or to drive the output transistors harder, neither of which were attractive in this project. Adding C180 looks like it cleans it up reasonably well with a single component. When the inputs transition, this cap pushes/pulls current in the opposite direction from the unwanted current associated with the Miller effect. If C180 is sized right, the result is a much nicer looking trapezoidal voltage waveform on the output. (Assuming with some capacitive loading, which was ensured by some of the output-protection parts not shown.)

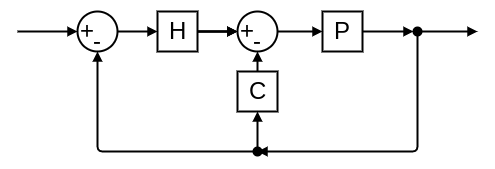

And here’s another convenient falstad simulation to play with, which isn’t entirely true to life, but can show the cross conduction effect going away.